#### **Introduction to the Architecture**

Suyash Tandon, Justin Chang, Julio Maia, Noel Chalmers, Paul T. Bauman, Nicholas Curtis, Nicholas Malaya, Alessandro Fanfarillo, Jose Noudohouenou, Chip Freitag, Damon McDougall, Noah Wolfe, Jakub Kurzak, Samuel Antao, <u>George Markomanolis</u>, Bob Robey

**Developing Applications with the AMD ROCm Ecosystem**

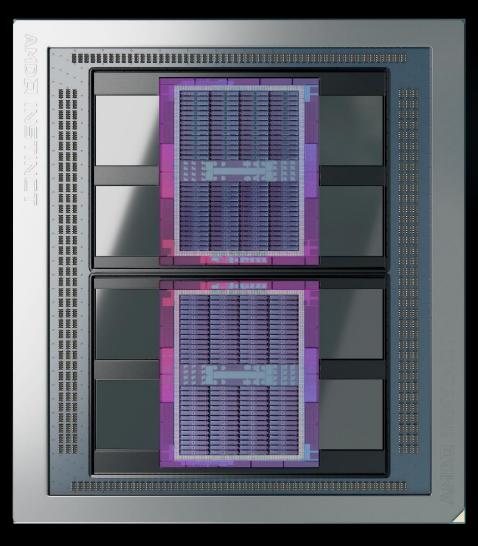

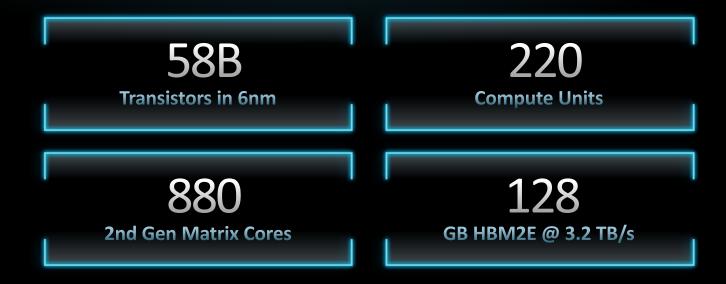

#### AMD INSTINCT™ MI250X

# WORLD'S MOST ADVANCED DATA CENTER ACCELERATOR

https://www.amd.com/system/files/documents/amd-cdna2-white-paper.pdf

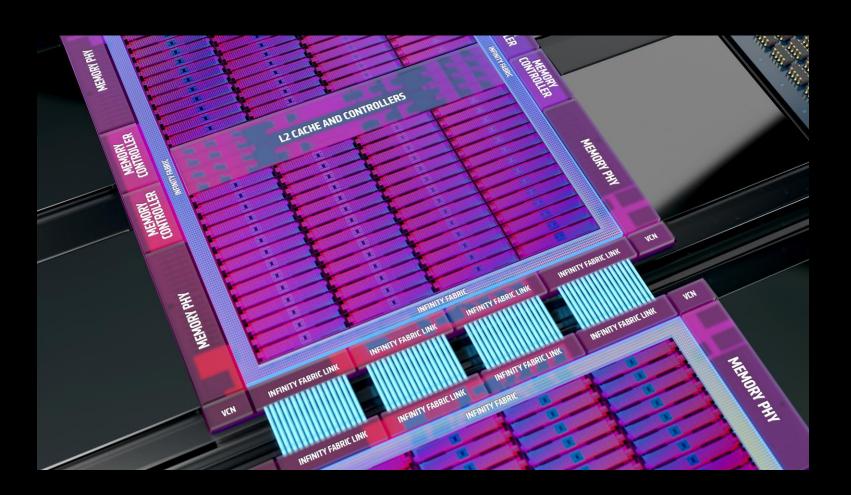

# MEMORY PHY COMPUTE ENGINE **COMPUTE ENGINE L2 CACHE AND CONTROLLERS MEMORY PHY** MEMORY PHY

#### 2ND GENERATION CDNA ARCHITECTURE

#### **TAILORED-BUILT FOR HPC & AI**

TSMC 6NM TECHNOLOGY

4 MATRIX CORES PER COMPUTE UNIT

8 INFINITY FABRIC LINKS PER DIE UP TO 110 CU PER GRAPHICS CORE DIE

MATRIX CORES ENHANCED FOR HPC

SPECIAL FP32 OPS FOR DOUBLE THROUGHPUT

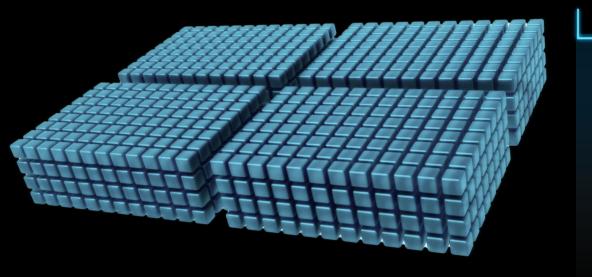

## **MULTI-CHIP DESIGN**

TWO GPU DIES IN PACKAGE TO MAXIMIZE COMPUTE & DATA THROUGHPUT

INFINITY FABRIC FOR CROSS-DIE CONNECTIVITY

> 4 LINKS RUNNING AT 25GBPS

400GB/S OF BI-DIRECTIONALBANDWIDTH

## 2<sup>nd</sup> GENERATION MATRIX CORES

OPTIMIZED COMPUTE UNITS FOR SCIENTIFIC COMPUTING

DOUBLE PRECISON (FP64)

MATRIX CORE THROUGHPUT

REPRESENTATION

#### MI100 MATRIX CORES

OPS/CLOCK/COMPUTE UNIT

No FP64 Matrix Core

256 FP32

1024 FP16

512 BF16

512 INT8

#### MI250X MATRIX CORES

OPS/CLOCK/COMPUTE UNIT

256 FP64

256 FP32

1024 FP16

1024 BF16

1024 INT8

## 2<sup>nd</sup> GENERATION MATRIX CORES

OPTIMIZED COMPUTE UNITS FOR SCIENTIFIC COMPUTING

- Current support for using MFMA instructions:

- AMD libraries: rocBLAS

- Intrinsics

- Inline assembly

- Not currently supported:

- Libraries of device functions, utilizing the matrix operations, that can be called from kernels

- Abstraction frameworks (Kokkos, Raja, OCCA)

- These would have to use one of the other mechanisms internally

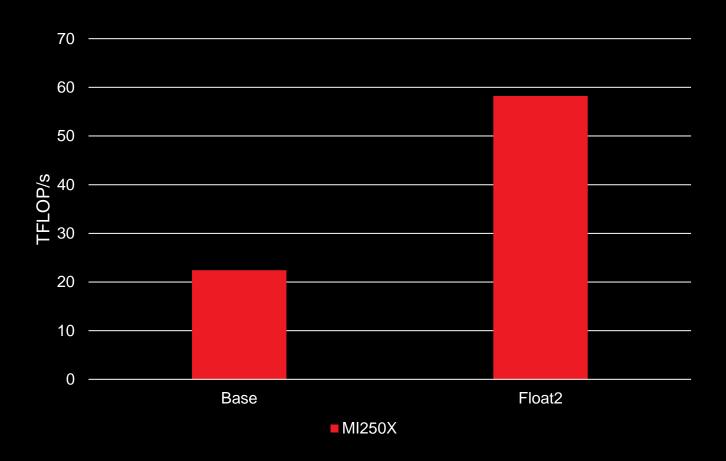

#### **NEW IN AMD INSTINCT MI250X**

#### PACKED FP32

FP64 PATH USED TO EXECUTE TWO COMPONENT VECTOR INSTRUCTIONS ON FP32

DOUBLES FP32 THROUGHPUT PER CLOCK PER COMPUTE UNIT

pk\_FMA, pk\_ADD, pk\_MUL, pk\_MOV operations

https://www.amd.com/en/technologies/infinity-hub/mini-hacc

#### From AMD MI100 to AMD MI250X

#### MI100

- One graphic compute die (GCD)

- 32GB of HBM2 memory

- 11.5 TFLOPS peak performance per GCD

- 1.2 TB/s peak memory bandwidth per GCD

- 120 CU per GPU

- The interconnection is attached on the CPU

AMD CDNA™ 2 white paper: https://www.amd.com/system/files/documents/amd-cdna2-white-paper.pdf

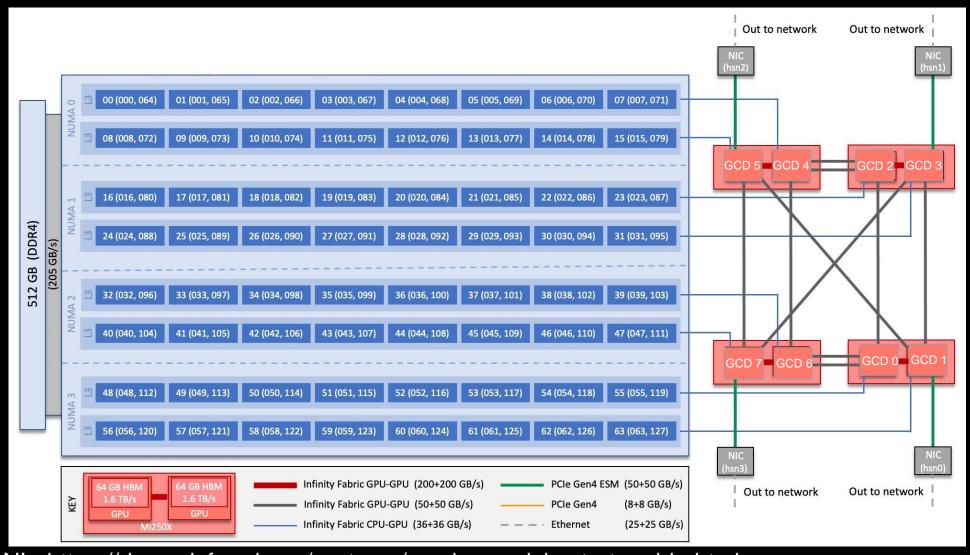

#### MI250X

- Two graphic compute dies (GCDs)

- 64GB of HBM2e memory per GCD (total 128GB)

- 26.5 TFLOPS peak performance per GCD

- 1.6 TB/s peak memory bandwidth per GCD

- 110 CU per GCD, totally 220 CU per GPU

- The interconnection is attached on the GPU (not on the CPU)

- Both GCDs are interconnected with 200 GB/s per direction

- 128 single precision FMA operations per cycle

- AMD CDNA 2 Matrix Core supports doubleprecision data

- Memory coherency

#### **LUMI – MI250X**

Credit: ORNL, <a href="https://docs.olcf.ornl.gov/systems/crusher\_quick\_start\_guide.html">https://docs.olcf.ornl.gov/systems/crusher\_quick\_start\_guide.html</a>

64-core AMD "Optimized 3rd Gen EPYC" CPU Core Chiplet Die connected to GCD via Infinity Fabric CPU-GPU

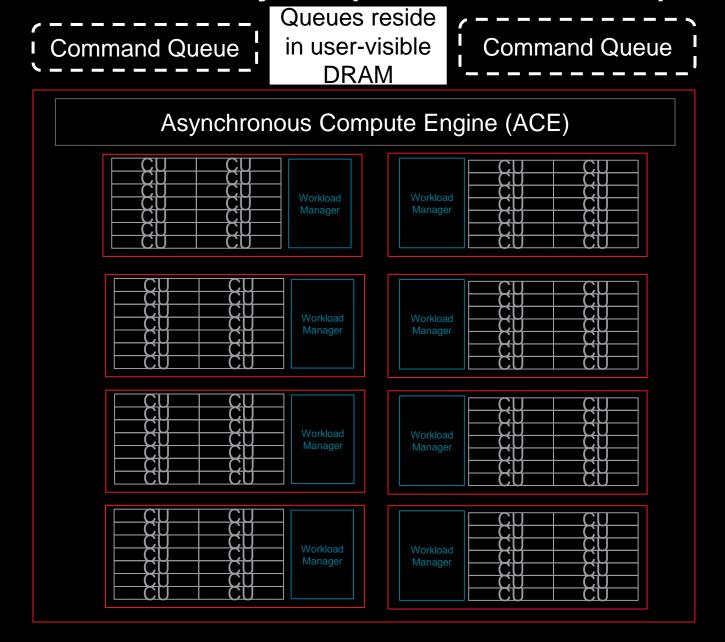

#### **AMD GCN GPU Hardware Layout (MI250X one GCD)**

Asynchronous Compute Engine (ACE) Shader Engine (SE0) Shader Engine (SE1) Shader Engine (SE3) Shader Engine (SE2) Shader Engine (SE4) Shader Engine (SE5) Shader Engine (SE6) Shader Engine (SE7)

### AMD GCN GPU Hardware Layout (MI250X one GCD)

#### **Disclaimer**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions, and typographical errors. The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. Any computer system has risks of security vulnerabilities that cannot be completely prevented or mitigated. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

THIS INFORMATION IS PROVIDED 'AS IS." AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS, OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY RELIANCE, DIRECT, INDIRECT, SPECIAL, OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Third-party content is licensed to you directly by the third party that owns the content and is not licensed to you by AMD. ALL LINKED THIRD-PARTY CONTENT IS PROVIDED "AS IS" WITHOUT A WARRANTY OF ANY KIND. USE OF SUCH THIRD-PARTY CONTENT IS DONE AT YOUR SOLE DISCRETION AND UNDER NO CIRCUMSTANCES WILL AMD BE LIABLE TO YOU FOR ANY THIRD-PARTY CONTENT. YOU ASSUME ALL RISK AND ARE SOLELY RESPONSIBLE FOR ANY DAMAGES THAT MAY ARISE FROM YOUR USE OF THIRD-PARTY CONTENT.

© 2022 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, AMD CDNA, AMD ROCm, AMD Instinct, and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.

# Questions?

#